반도체 소자를 더 작고 촘촘하게 만들기 위한 글로벌 미세 공정 경쟁이 물리적 한계에 다다른 가운데 국내 연구진이 평면 기판의 앞면과 뒷면 모두에 회로를 새겨 넣는 혁신적인 공정 기술을 개발했다.

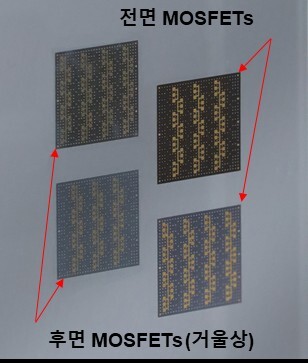

포항공과대학교(이하 포스텍) 기계공학과 김석 교수와 통합과정 이상엽 씨 연구팀은 머리카락 굵기의 10분의 1 수준인 초박막 실리콘 기판 양면에 반도체의 핵심 소자인 ‘MOSFET(금속 산화막 반도체 전계 효과 트랜지스터)’을 정밀하게 구현하는 데 성공했다고 27일 밝혔다.

그동안 반도체 업계는 회로 선폭을 줄여 성능을 높여왔으나 평면(2D) 구조에서는 더 이상 공간을 확보하기 어려운 상황에 직면해 왔다.

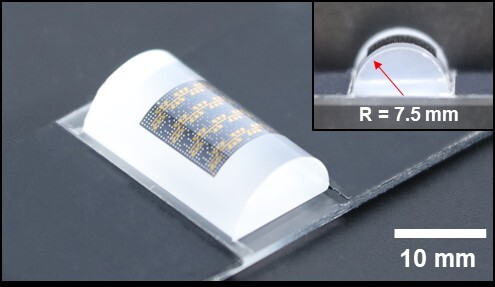

이에 반도체를 위로 쌓는 3차원 집적 기술이 대안으로 떠올랐고 얇고 유연한 ‘초박막 실리콘’이 핵심 소재로 주목받았다.

하지만 기판이 너무 얇아 공정 중 쉽게 깨지거나 뒤틀리는 탓에 양면을 모두 활용하는 것은 불가능에 가깝다고 여겨졌다.

연구팀은 특정 용액과 중간 기판을 활용해 초박막 실리콘의 안정성을 확보하는 특수 공정 전략을 개발해 이 난제를 해결했다.

실험 결과, 기판의 한 면만 사용할 때보다 반도체 소자를 2배 더 많이 배치할 수 있었으며 1만 번 이상의 반복 굽힘 시험 후에도 파손 없이 정상 동작하는 등 뛰어난 내구성을 증명했다.

이번 기술은 고성능 3차원 반도체뿐만 아니라 폴더블 스마트폰, 웨어러블 전자기기, 차세대 의료용 센서 등 유연성이 필요한 첨단 기기 분야에 폭넓게 적용될 전망이다.

김석 교수는 “이번 성과는 반도체 설계의 패러다임을 바꿀 수 있는 새로운 선택지를 제시한 것”이라며 “더 작은 공간에 더 많은 연산 기능을 담아야 하는 차세대 반도체 시장에서 핵심적인 역할을 할 것으로 기대한다”고 말했다.

이번 연구 결과는 ‘인터내셔널 저널 오브 익스트림 매뉴팩처링(IJEM)’에 게재됐다.

/단정민기자 sweetjmini@kbmaeil.com